Nebezpečí pro integrované obvody (IO) při osazování DPS

Snížení odolnosti integrovaných obvodů vůči ESD

Díky menším rozměrům polovodičových prvků a stále hustšímu osazování DPS jsou integrované obvody prokazatelně méně odolné vůči ESD. Příkladem můžou být:

- snímací (MR) hlavy, používané na harddiscích. Ty byly představeny v polovině roku 1990 a jejich ESD citlivost se snížila z 1000V na méně než 20V zdánlivě přes noc.

- čip v RF čtečkách, který je menší než zrnko písku, ale přesto obsahuje všechny funkce, které obsahoval čtyřnásobně velký čip před dvěma lety. CCD technologie je na hranici svých možností. Vzdálenosti pixelů jsou nyní jen 90nm a očekává se zkrácení této vzdálenosti i pod 45nm. Vzhledem k citlivé povaze polovodičového materiálu jsou RF aplikace náchylné k poškození i těmi nejmenšími statickými náboji. – jedná se konkrétně o arsenikový materiál (GaAs) a křemík s germaniem (SiGe). Zhruba 30% poškození mobilních telefonů může mít ESD příčiny.

Na Obr. 1 ve fotogalerii níže naleznete graf, kde se se snížením pracovního napětí IO snižuje také napětí, při kterém může dojít k poškození IO.

Menší rozměry IO mají nepříznivý dopad na schopnosti IO přežít ESD (elektrostatický výboj) a EOS (elektrostatické přepětí). Ukázkovým příkladem je vývoj nMOS tranzistorů v CMOS technologii. Některé změny, které snižují schopnost nMOS přežít ESD jsou uvedeny v následující tabulce:

| Vývojová změna nMOS | Důvod pro zavedení změny | Dopad na ESD |

|---|---|---|

| Mělčí spoje | Kratší kanál, velikost tranzistoru | Nebezpečnější důsledky ESD |

| Méně dotovaný kanál | Omezení teplotní degradace tranzistoru | Snížení proudové zatížitelnosti |

| Silicodové spoje | Snížení odporu tranzistoru | Snížení proudové zatížitelnosti |

| Snížení oxidace hradel | Zvýšení výkonu tranzistoru | Snížení napětí, při kterém dochází k poškození oxidy |

Ochranné prvky na DPS

Po osazení obvodu je čip spojen s dalšími prvky na desce. Tím se výrazně snižuje pravděpodobnost poškození. Na DPS totiž většinou existují nízkoimpedanční prvky. Po instalaci obvodů nebývají integrované ochrany těchto prvků už použity.

Integrované obvody však mohou být v jiném případě vystaveny účinkům elektrického přepětí (EOS). Během EOS mohou být neúmyslně aktivovány i obvody ESD ochrany. Vedení proudu při EOS je často velké a dlouho trvající. V některých případech znamená vytváření nebezpečného množství tepla uvnitř čipu. Důsledkem toho dochází k nevratným a rychlým poškozením systému (např. roztavení pouzdra obvodu). Spolehnout se na integrované obvody ESD jako na ochranu před EOS není žádoucí, i když v některých případech poskytují dostatečnou ochranu. Plně funkční IO může být poškozen ve chvíli, kdy jsou do aplikace přivedeny vstupní signály.

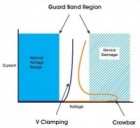

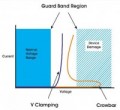

Ochranné prvky musí být uzavřeny do obvodů IO. Všechny výstupy IO mají určitý rozsah provozního napětí, jak je znázorněno na Obr. 2.

Mimo určený rozsah napětí je bezpečné pásmo. Napětí mimo toto bezpečné pásmo bude iniciovat poškození IO. Jak jsou používány čím dál více pokročilé technologie, a snižuje se provozní napětí, šířka ochranného pásna se snižuje také. ESD ochrana součástky musí pracovat v rámci ochranného pásma, jak je právě patné z obrázku 2. Užší ochranné pásmo vyžaduje ochranné prvky s nižším odporem v jejich otevřeném „ON“ stavu. Vývoj v elektroprůmyslu směřuje ke snížení svodového napětí.

Trendy ESD citlivosti součástek

Tři grafy ve fotogalerii níže ukazují trendy ESD citlivosti součástek založené na 3 ESD modelech:

- Graf 1 Model lidského těla – Human Body Model (HBM)

- Graf 2 Model strojový – Machine Model (MM)

- Graf 3 Model nabíjené součástky – Charge Device Model (CDM)

Z výzkumu ESD Asociace v New Yorku vyplývá, že vzhledem ke zvyšující se citlivosti elektrostaticky citlivých součástek, musí být splněny následující požadavky:

Normy dnes udávají běžně používané hodnoty rezistance systému osoba-uzemňovací náramek nebo systému osoba-obuv-podlaha. Konkrétně je to hraniční hodnota 35MOhm, která však předpokládá nakládání s výrobky s minimální citlivostí na ESD 100V. Při citlivosti nižší než 100V musí být také rezistance vůči zemi také nižší. Např. pro výrobky s citlivostí 50V by měla být na testeru náramků nastavena hraniční hodnota 20MOhm.

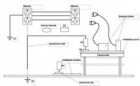

Pro doplnění problematiky uvádíme na Obr. 3 schéma správného uzemnění v EPA.

► Nákup na www.abetec.cz

► Další odborné články

► e-Shopy, školení a e-Booky

|

soldering.cz |

e Booky ZDARMA |

fotografie |

video |